Faculty of Information Technology and Communication Sciences (ITC), Embedded Systems / Customizable Processors Group

A Finnish research team at Tampere University has created an open-source toolset that makes it much easier to add custom instructions to RISC-V processors.

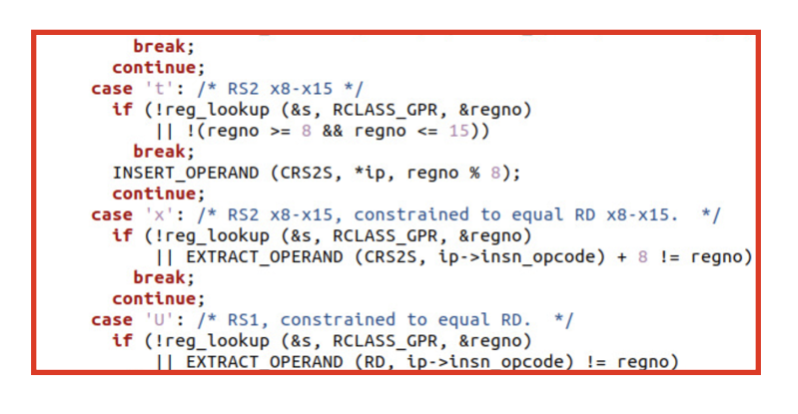

The idea is simple: you describe the new instruction once, and the system automatically generates both the hardware coprocessor and the compiler support needed to use it. Because the accelerator connects through standard sockets, the processor itself does not need to be modified, reducing verification work. Tests show strong results—programs ran up to 40% faster with only small area and timing overhead. This approach offers a practical, low-risk way to boost performance in many RISC-V-based systems.

Tampere University hosts one of Europe’s leading open-source processor research groups, focusing on RISC-V extensions, accelerator interfaces, and compiler–hardware co-design. The team has developed a novel flow that automatically generates both custom-instruction hardware and compiler support from a single description, enabling significant speedups on widely used RISC-V cores while keeping verification costs low.

Here are the research Individual Researchers that have been leading this important and complex project:

- Pekka Jääskeläinen – Associate Professor

A pioneer in customizable processor architectures and HW/SW co-design. Leads Tampere University’s work on open RISC-V cores, accelerator interfaces, and compiler technologies. His group’s contributions underpin several international open-source initiatives, including OpenASIP and RISC-V extension tooling.

- Kari Hepola – Doctoral Researcher

Specializes in automatic hardware generation and LLVM retargeting for custom instructions. Principal technical contributor to the new toolchain described in the article, with work spanning accelerator wrappers, code generation, and performance evaluation on CVA6 and Rocket cores.

- Jarmo Multanen – Researcher

Focuses on accelerator design, interface integration (CVXIF/RoCC), and synthesis/timing analysis. His work ensures that the generated hardware modules remain area-efficient and compatible with existing open-source RISC-V ecosystems, such as CVA6 and Chipyard.

- Tharaka Ranasinghe Arachchige – Doctoral Researcher

Works on hardware–software interfaces, instruction semantics modelling, and out-of-order commit logic for accelerator channels. Contributed to the toolset’s instruction-tracking mechanisms and multi-latency coprocessor support across different RISC-V socket standards.

Here is the link to a full technical summary of the project with full sources…